Si dice multivibratore un circuito in grado di generare in uscita una forma d'onda di tipo rettangolare. Vi sono tre tipi di multivibratori. Multivibratore monostabile, multivibratore bistabile, multivibratore astabile.

Un multivibratore si dice monostabile quando ha un solo stato stabile, cioè normalmente l'uscita si trova a livello alto oppure a livello basso; quando arriva un impulso dall'esterno il monostabile commuta, cioè se si trovava a livello alto passa a livello basso; però finito l'effetto dell'impulso esterno, torna nello stato precedente.

Un multivibratore si dice bistabile quando ha due stati stabili, cioè normalmente l'uscita si trova a livello alto oppure a livello basso; quando arriva un impulso dall'esterno il monostabile commuta, cioè se si trovava a livello alto passa a livello basso e viceversa; finito l'effetto dell'impulso esterno, rimane nello stato determinato dall'impulso.

Un multivibratore si dice astabile quando commuta continuamente dallo stato alto a quello basso, senza ricevere impulsi dall'esterno.

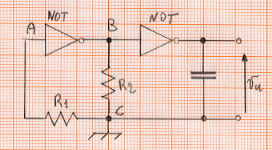

Un semplice multivibratore astabile si può realizzare con le porte logiche, come nel seguente circuito:

Come si vede vi sono due porte NOT, che danno in uscita un segnale opposto a quello ricevuto al loro ingresso, collegate in modo che l'uscita di una sia l'ingresso dell'altra.

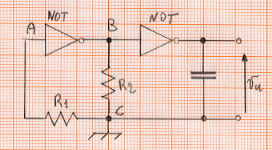

Supponiamo che all'istante iniziale il condensatore C sia scarico. Il primo NOT riceve uno zero logico in ingresso e dà in uscita sul punto B il valore 1. Il secondo NOT riceve 1 in ingresso e da in uscita zero. Il condensatore C è costretto a caricarsi, col positivo verso il basso, tramite la resistenza R2. Quando la tensione del condensatore è cresciuta fino a raggiungere il livello logico 1, sul primo NOT viene applicato il livello logico 1, tramite R1, sul punto A; sul punto B ottengo livello logico 0; in uscita ho livello logico 1. Il condensatore C è costretto a scaricarsi e caricarsi con segno opposto, cioè col positivo verso l'alto, riducendo la tensione sul punto A. Quando la tensione sul punto A raggiunge lo 0 logico, il punto B si porta a 1, e l'uscita a 0, riprendendo il ciclo iniziale. La forma d'onda in uscita sarà la seguente:

Per calcolare la frequenza, prima ci calcoliamo il periodo con la formula:

T1 = T2 = 1,1 R2 C

Dove T1 è il tempo in cui l'uscita si mantiene a livello alto; T2 è il tempo in cui l'uscita si mantiene a livello basso.

Tale formula è valida per porte logiche tipo CMOS. Poi ci calcoliamo :

f = 1

T

Il timer è un circuito integrato complesso avente lo scopo di regolare per un tempo prestabilito determinati circuiti. In pratica il timer 555 è un temporizzatore. Nella seguente figura vediamo una vista esterna.

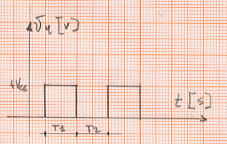

Lo schema a blocchi del circuito integrato è il seguente:

Possiamo notare tre resistori uguali da 5 kW , aventi lo scopo di dividere la tensione di alimentazione Vcc in tre tensioni multiple di 1/3 di Vcc; in fatti tra il resistore inferiore e massa, cioè sul morsetto non invertente del secondo comparatore, abbiamo una tensione pari a Vcc/3; tra il secondo resistore e massa, cioè sul morsetto invertente del primo comparatore, abbiamo una tensione pari a 2Vcc/3; infine sul terzo resistore dal basso abbiamo tutta la Vcc. Tali tensioni ci servono come tensioni di riferimento per i due comparatori interni.

Infatti vi sono due comparatori; il primo comparatore, quello superiore ha una tensione di riferimento sul morsetto invertente pari a 2Vcc/3, mentre il morsetto non invertente è disponibile all'esterno dell'integrato, sul piedino 6, detto soglia. In pratica quando la tensione sul piedino 6 è maggiore di 2Vcc/3 l'uscita del primo comparatore si porta a livello logico alto, cioè 1; quando, invece, la tensione sul piedino 6 è inferiore a 2Vcc/3 l'uscita del primo comparatore si porta a livello basso, cioè zero.

Viceversa, il secondo comparatore , quello inferiore, ha una tensione di riferimento sul morsetto non invertente pari a Vcc/3, mentre il morsetto invertente è disponibile all'esterno dell'integrato, sul piedino 2, detto trigger. In pratica quando la tensione sul piedino 2 è maggiore di Vcc/3 l'uscita del secondo comparatore si porta a livello logico basso, cioè 0; quando, invece, la tensione sul piedino 2 è inferiore a Vcc/3 l'uscita del secondo comparatore si porta a livello alto, cioè 1.

Le uscite dei due comparatori sono applicate in ingresso ad un latch di tipo S-R.

Il latch di tipo S-R è un circuito logico con due ingressi e due uscite. Un primo ingresso, detto SET, cioè porre a 1, quando si trova a 1, obbliga l'uscita Q a portarsi a 1; il secondo ingresso, detto RESET, cioè azzerare, quando si trova a livello logico 1, porta l'uscita Q a zero, cioè l'azzera. La tabella di verità è la seguente:

|

S |

R |

Q |

Q |

| 0 | 0 | Q | Q |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 |

indeterminato |

indeterminato |

Nel timer 555 delle due uscite l'uscita Q non viene utilizzata, ma viene usata solo l'uscita Q negato. Se Q negato si trova a livello alto, manda in saturazione il transistor e quindi il piedino 7 viene collegato a massa, permettendo la scarica di un condensatore, che di solito viene applicato al piedino 7; se invece l'uscita Q negato si trova a livello basso il transistor è interdetto, quindi il piedino 7 si trova isolato da massa, permettendo la carica del condensatore. Sull'uscita Q negato è applicato un invertitore, che trasforma l'uscita Q negato in uscita Q, ed inoltre permette una elevata corrente in uscita. Il timer 555 può essere utilizzato sia come multivibratore astabile, che come bistabile.

MULTIVIBRATORE ASTABILE CON TIMER NE 555

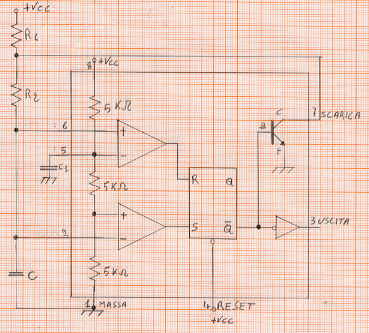

Il multivibratore astabile è un circuito in grado di generare una forma d'onda rettangolare, senza segnale applicato in ingresso. Lo schema elettrico è il seguente:

Supponiamo che inizialmente il condensatore C sia scarico, gli ingressi dei due comparatori sui piedini 2 e 6 si trovano a livello basso; il comparatore superiore dà in uscita un livello basso, quindi R=0; il comparatore inferiore dà in uscita un livello alto, quindi S=1; il latch S-R pone l'uscita Q a 1, mentre Q negato = 0; l'uscita del timer, sul piedino 3 si trova a livello alto; il transistor è interdetto, perché la base non è polarizzata direttamente, il piedino 7 si trova isolato da massa, il condensatore C inizia a caricarsi attraverso i resistori R1 ed R2 che si trovano in serie.

Quando la tensione ai capi del condensatore C raggiunge il calore di Vcc/3, il comparatore inferiore commuta e si porta a livello basso, S=0; i latch S-R non commuta perché anche R=0, e quindi la parte restante del circuito resta nello stato precedente, ed il condensatore continua a caricarsi. Quando la tensione ai capi del condensatore C raggiunge i 2Vcc/3 allora il comparatore superiore commuta, portando la sua uscita a livello alto; R=1; il latch S-R azzera la sua uscita Q; Q negato = 1; l'uscita dell'integrato si porta a livello basso; il transistor va in saturazione, mettendo il piedino 7 del timer a massa; il condensatore è costretto a scaricarsi attraverso il solo resistore R2.

Quando la tensione del condensatore C scende al di sotto di Vcc/3 allora il comparatore inferiore commuta, portando S a 1, mentre R già era a zero appena iniziata la scarica; quindi il latch S-R avendo S=1 porta la sua uscita Q a 1, e Q negato a 0; l'uscita del timer si porta a livello alto; il transistor è interdetto, il piedino 7 è staccato da massa, il condensatore inizia a ricaricarsi, ripetendo il ciclo precedente.

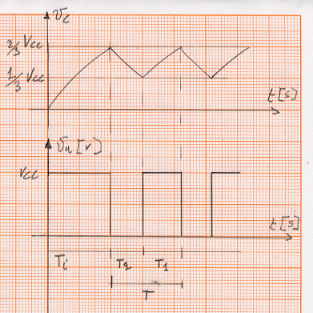

I diagrammi sono i seguenti:

Trascurando il tempo iniziale di carica Ti, in cui il condensatore parte da tensione zero, indichiamo con T1 il tempo in cui l'uscita si mantiene a livello alto, ed il condensatore si carica; T1 lo possiamo calcolare con la seguente formula:

T1 = 0,693 (R1+R2) C

Infatti il condensatore si carica attraverso R1 ed R2.

Indichiamo con T2 il tempo in cui l'uscita si mantiene a livello basso; T2 lo possiamo calcolare con la seguente formula:

T2 = 0,693 R2 C

Sommando i due tempi T1 e T2 otteniamo l'intero periodo cioè

T = T1 + T2

La frequenza sarà l'inverso del periodo, cioè

f = 1

T

Si dice ciclo utile D il rapporto tra T1 e T, cioè

D = T1

T

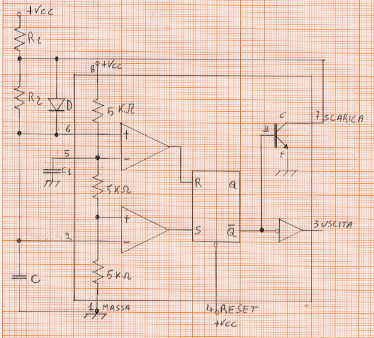

Notiamo che è difficile ottenere un ciclo utile pari al 50%, cioè T1 = T2, cioè il tempo in cui la forma d'onda è a livello alto è uguale al tempo in cui la forma d'onda è a livello basso; per ottenere questo dovremmo porre R2 = 0; però R2 è la resistenza di collettore del transistor interno, che non può avere valori inferiore a 1.000 W , per evitare di bruciare il transistor. Per ottenere R2 = 0 si può mettere in parallelo ad R2 un diodo, secondo il seguente schema:

in tal modo durante la carica del condensatore C il diodo D è polarizzato direttamente e si comporta come un corto circuito, il condensatore si carica solo attraverso R1; durante la scarica del condensatore il diodo è polarizzato inversamente, quindi è come un circuito aperto, permettendo al condensatore di scaricarsi attraverso R2.

Il condensatore C1 serve come livellamento della tensione di riferimento. Il morsetto di RESET va collegato a + Vcc, in modo da escluderlo.

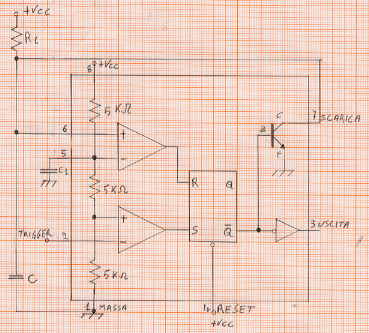

MULTIVIBRATORE MONOSTABILE CON TIMER 555

Il multivibratore monostabile genera una forma d'onda rettangolare in uscita, però ha bisogno di un impulso esterno per poterla generare. Lo schema elettrico è il seguente:

Il monostabile ha un solo stato stabile, nel nostro caso l'uscita si mantiene sempre a livello basso finché non arriva un impulso dall'esterno, sul piedino 2. Infatti mantenendo a livello alto il piedino 2, il comparatore inferiore dà in uscita un valore basso; quindi S=0; invece il comparatore superiore, essendo il condensatore inizialmente scarico, dà in uscita 0; quindi R=0; quindi il latch S-R resta nella condizione di azzeramento, cioè Q=0; Q negato =1; l'uscita del timer è zero; il transistor va in saturazione, essendo la base polarizzata direttamente, il piedino 7 si trova a massa, ed il condensatore C non si può caricare attraverso R. Il circuito si mantiene stabile con uscita a livello basso.

Quando arriva un impulso dall'esterno sul piedino 2, detto trigger, la tensione sul piedino 2 si porta a zero, il comparatore inferiore dà in uscita un livello alto; S=1; mentre R è rimasto a 0; immediatamente l'uscita Q del latch S-R si porta a 1, mentre Q negato =0; l'uscita del timer si porta a 1; il transistor è interdetto, il condensatore inizia a caricarsi attraverso il resistore R1; quando la tensione sul condensatore raggiunge i 2Vcc/3 il comparatore superiore commuta portando l'uscita a livello alto, quindi R = 1; mentre il comparatore inferiore ha già dato l'uscita a livello basso non appena il condensatore ha superato Vcc/3; quindi S = 0; l'uscita del latch S-R si azzera, quindi Q = 0; Q negato = 1; l'uscita del timer si porta a livello basso; il transistor va in saturazione scaricando il condensatore.

Il condensatore C1 serve come livellamento della tensione di riferimento. Il morsetto di RESET va collegato a + Vcc, in modo da escluderlo.

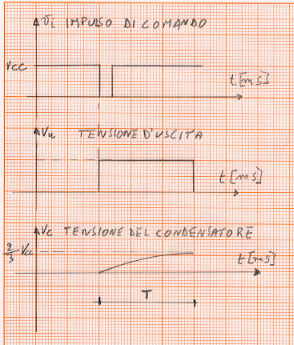

I diagrammi sono i seguenti:

Indichiamo con T il tempo in cui il condensatore si carica, si ha che:

T = 1,1 R1C